Каталог оборудования

-

Устройства для модернизации УЧПУ НЦ31 и МС2109

- УЧПУ "Электроника НЦ3110Р"

- Плата расширения электроавтоматики КЕ-16

- Контроллер КС16АК20

- Контроллер КС1В340

- Контроллер КС1325

- Кассета внешней памяти КВП10 USB

- Программатор для подключения КВП10 USB к ПК

-

Модернизация станков с УЧПУ МС2101, МС2106, НЦ80

- Модернизация платы памяти 3100 УЧПУ МС2101, МС2106, НЦ80

- Эмулятор кассеты ЦМД

-

Устройства ввода-вывода для замены перфоленты, магнитной ленты, дискет

- Терминал ввода-вывода ТВВ-02М

- Терминал ввода-вывода ТВВ-01См

- Терминал-эмулятор дисковода ТЭД-03b USB

Внутрисхемный тестер ВТ-02

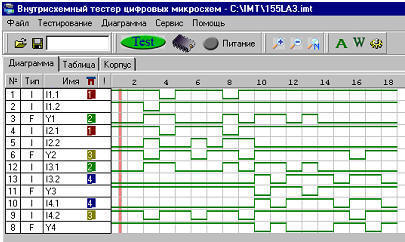

.bmp) Внутрисхемный тестер цифровых микросхем ВТ-02 предназначен для внутрисхемного контроля функционирования цифровых интегральных микросхем в электронных модулях с напряжением питания 5 вольт. Прибор работает в составе автоматизированной системы диагностики «ТЕСТ-Д», что расширяет функциональные возможности системы и является её логическим продолжением.

Внутрисхемный тестер цифровых микросхем ВТ-02 предназначен для внутрисхемного контроля функционирования цифровых интегральных микросхем в электронных модулях с напряжением питания 5 вольт. Прибор работает в составе автоматизированной системы диагностики «ТЕСТ-Д», что расширяет функциональные возможности системы и является её логическим продолжением.

Тестер ВТ-02 имеет 32 цифровых канала, по которым происходит подача воздействий на проверяемую микросхему и приём реакций на эти воздействия. Принимаемые сигналы анализируются по уровням логического нуля и единицы, которые задаются пользователем. Проверяемая микросхема подключается при помощи тестового зажима (клипсы), соответствующего типу ее корпуса (DIP, SOIC и др.), а ее питание двумя зажимами, подключенными к цепи питания тестируемой платы.

Технические параметры

Количество информационных каналов - 32

Уровень логической единицы выходного сигнала не менее - 2,4 В

Уровень логического ноля выходного сигнала не более - 0,4 В

Максимальный ток выходного сигнала - от -300 мА до +300 мА

Максимальная аппаратная глубина тестирования - 8192 такта

Время такта - от 1 до 8 мкС

Дискретизация такта - 1 мкС

Диапазон измерения статических напряжений на каналах - от -1,38В до+5,00 В

Дискретизация измерения - 25 мВ

Количество зон анализа по уровню принимаемых сигналов - 2

Диапазон зоны - от 0 до 5 В

Дискретизация зоны - 20 мВ

Напряжение питания объекта контроля - от 4,75 В до 5,25 В

Максимальный ток объекта контроля - 4,5А

Напряжения питания устройства +5 В,-5 В,+12 В,-12 В

Внутрисхемный тестер цифровых микросхем ВТ-02 использует метод цифрового внутрисхемного тестирования (английская аббревиатура - ICFT ). Этот метод позволяет, не выпаивая цифровые микросхемы из платы, проверить правильность их функционирования. Для этого на контакты тестируемой микросхемы подаются мощные импульсы, способные установить заданный уровень логического сигнала независимо от логического состояния компонента связанного с проверяемым контактом (метод подавления логических уровней устройства -'backdriving'). Величина импульса тока, подаваемого на контакт микросхемы, является достаточной для принудительной установки выхода логического элемента в заданное состояние и в то же время не выводит его из строя. Для того, чтобы ограничить рассеиваемую мощность элемента микросхемы, время, в течение которого подается воздействие, ограничено. Согласно рекомендации международного стандарта INT DEF SID 0053-1 время перегрузки не должно превышать 65 миллисекунд.

Тестирование микросхемы выполняется в 3 этапа:

1. Подача напряжения питания на проверяемое устройство, измерение напряжений на выводах микросхемы с проверкой контактирования клипсы с выводами микросхемы и ориентации клипсы по отношению к ключу микросхемы.

2. Проверка исходных логических состояний выводов микросхемы и наличие на них переключений (сигналов от внутреннего генератора тестируемого устройства), наличие выводов, подключенных к цепям питания, и выводов, соединённых между собой перемычками. Полученный результат выводится на дисплей в виде мнемосхемы объекта контроля.

3. По результату второго этапа проверки программа автоматически изменяет заданный в тесте алгоритм тестирования, производит проверку микросхемы в соответствии с измененным алгоритмом и выводит результаты тестирования на экран монитора в виде временных диаграмм и таблицы данных.

При помощи тестера имеется возможность выполнять проверку различных цифровых микросхем, включая микросхемы ОЗУ и ПЗУ. Следует подчеркнуть, что данный прибор имеет возможность считать информацию с микросхем ППЗУ, впаянных в платы. Это особенно актуально сегодня, т. к. большая часть микросхем ППЗУ, установленных на промышленном оборудовании, выработало свой ресурс и может в любой момент выйти из строя.

В комплект поставки тестера входит библиотека тестов микросхем различных серий и справочник аналогов, где каждому тесту микросхемы прилагается перечень аналогов микросхем разных серий, стран и производителе й.

В состав программного обеспечения входит редактор тестов. С его помощью пользователь имеет возможность самостоятельно изменять алгоритм тестирования микросхем и производить разработку и отладку тестовых программ на микросхемы, отсутствующие в базовой библиотеке. Методика составления тестов на микросхемы проста и доступна любому специалисту-электронику.

.jpg)